MOSFETの寄生容量の概算方法について.

本記事では,手計算で見積もることの多いゲート容量とドレイン容量を取り上げる.

寄生容量の概算

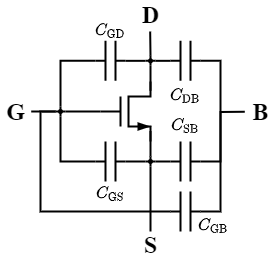

MOSFETの寄生容量は次に示すように各端子にある.

手計算で見積もることの多いゲート容量とドレイン容量を取り上げる.

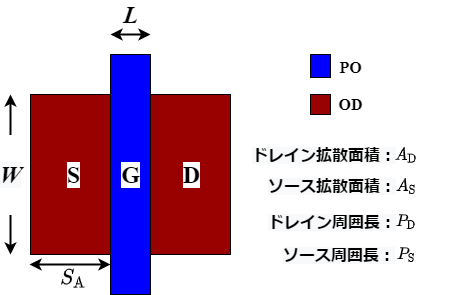

今回考えるMOSFETのレイアウトは次の図に示すシンプルなものとする.

ドレイン容量

ソースとバルクが同電位であるとすると,ドレイン容量は上の図の$C_{\rm DB}$ である.

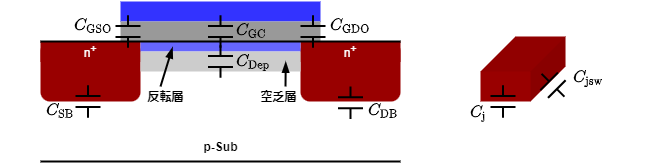

この容量は,下の図のようにn+とバルク間の底面の容量と側壁の容量に分けられ,次のように表せる.

$$ C_{\rm D} = A_{\rm D} C_{\rm j} + P_{\rm D} C_{\rm jsw} $$

次の表に各変数の意味をまとめる.

$S_{\rm A}$は上のMOSFETのレイアウトの図を参照.

| 変数名 | 意味 |

|---|---|

| $A_{\rm D} = S_{\rm A} W$ | ドレイン拡散面積 |

| $P_{\rm D} = 2(W+S_{\rm A})$ | ドレイン周囲長 |

| $C_{\rm j}~~{\rm [F/m^2]}$ | ドレイン底面の単位面積あたりの容量 |

| $C_{\rm jsw}~~{\rm [F/m]}$ | ドレイン側壁の単位長あたりの容量 |

※底面は単位面積あたり,側壁は単位長あたりの容量であることに注意!

よって,第1項の$A_{\rm D} C_{\rm j}$が底面による容量,第2項の$P_{\rm D} C_{\rm jsw}$が側壁による容量である.

$C_{\rm j}, ~C_{\rm jsw}$はプロセスによって決まる値でモデルファイルなどに記述されている.

これらの値を使って概算するのが良いだろう.

ゲート容量

MOSFETの容量は各ノード間の電圧によって変化するため非常に複雑である.

しかし,ドレインとソースを接地している状況下ではシンプルに捉えることができる.

集積回路では精度のいらない容量にはゲート容量を用いる場合が多いため,ドレイン・ソースをともに接地した状態のゲート容量の特性は重要である.

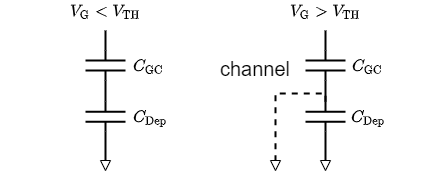

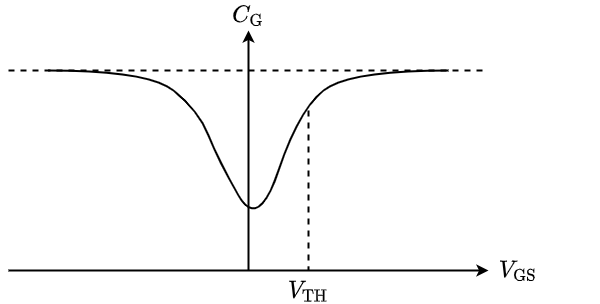

$V_{\rm GS} > V_{\rm TH}$でチャネルが形成されているときは,通常の平行平板の容量となるので,

$$ C_{\rm G} = WL\frac{\varepsilon_{\rm OX} \varepsilon_0}{t_{\rm OX}} ~~~ (V_{\rm GS} > V_{\rm TH}) $$

$t_{\rm OX}$は酸化膜の厚さ,$\varepsilon_{\rm OX}$は酸化膜の比誘電率である.

一方で,$V_{\rm GS} < V_{\rm TH}$のときはチャネルが形成されていないため,酸化膜の容量と空乏層容量の直列となる.

一般的に空乏層容量の方が小さいため,$V_{\rm GS} < V_{\rm TH}$のときのほうが容量が小さい.

これらの状態は回路図的には,チャネルによって空乏層容量$C_{\rm GC}$の下側のノードがチャネルによってソースに接続されるかされないで表せる.

$V_{\rm GS} < 0$のときは,MOSFETが蓄積状態で動作するため,酸化膜の容量となる.

以上を踏まえ,横軸に$V_{\rm GS}$をとりゲート容量の概形を書くと次のようになる.

まとめ

MOSFETのドレイン容量はドレインの底面容量と側壁容量を考えればよく,

$$ C_{\rm D} = A_{\rm D} C_{\rm j} + P_{\rm D} C_{\rm jsw} $$

となる.

MOSFETのゲート容量は,ドレインとソースが同電位で$(V_{\rm GS} > V_{\rm TH})$のとき,

$$ C_{\rm G} = WL\frac{\varepsilon_{\rm OX}}{t_{\rm OX}} ~~~ (V_{\rm GS} > V_{\rm TH}) $$

で概算でき,$V_{\rm GS} < V_{\rm TH}$のときは空乏層容量が見えるので容量値は小さくなる.

参考文献

[1] Behzad Razavi(2003),「アナログCMOS集積回路の設計」,丸善出版.

[2] LSI設計者のためのCMOSアナログ回路入門(2017),「LSI設計者のためのCMOSアナログ回路入門」,CQ出版社.