本記事ではVerilogの導入として,Verilogが何なのかとどういうときに使われるものなのかを説明する.

Verilogとは

VerilogはHDL(Hardware Description Language)の1種で,主に論理回路の記述に用いられる.

論理回路には大きく分けて2種類あって,

- 組み合わせ回路

- 順序回路

がある.それぞれについて具体例を挙げて見ていく.

Verilogによる論理回路の記述

組み合わせ回路はNOTゲートやANDゲート,ORゲートなどによって論理演算を行う回路で,現在の入力だけで出力結果が決まる論理回路を指す.

次に簡単なVerilogのコードを示してみた.

上部は入出力の定義で下部が論理の記述であり,ANDやOR,セレクタ(11行目の3項演算子)などが簡単に表せる.

本来NOTゲートなどの論理ゲートはMOSFET数個で構成されるため,簡単な論理を実現するのにも結構な苦労になる.

そこで,Verilogのような手軽に論理を表すことができるツールが重宝されるのである.

module module1 (

input a_i,

input b_i,

input c_i,

output z_o

);

//assign z_o = a_i && b_i; // AND

//assign z_o = a_i || b_i; // OR

//assign z_o = a_i && !b_i;

assign z_o = c_i ? a_i : b_i;

endmoduleVerilogによる順序回路の記述

順序回路は組み合わせ回路とは異なり,現在の入力だけでは出力結果が決まらず過去の入力も出力に影響する論理回路である.

例を挙げれば,キーロックのようなシステムが想像が付きやすい.

1⇒2の順に打ち込まないと開かないロックを論理回路で実現する場合は順序回路である.

なぜなら,過去にどの数字が押されたかの記録がないと判断が付かないからだ.

そこで,順序回路には過去の入力データを保存するレジスタが必要となる.

ディジタル回路でこの役割を担うのがフリップフロップだ.

このフリップフロップもMOSFETで実現しようとすると少し面倒となるが,Verilogではregのみで良い.

良く用いられるフリップフロップは,データを更新するタイミングとして一定周期のクロック信号が必要となる.

Verilogでは,always @(posedge clk_i)のような記述があり,この中に値の更新動作を記述する.

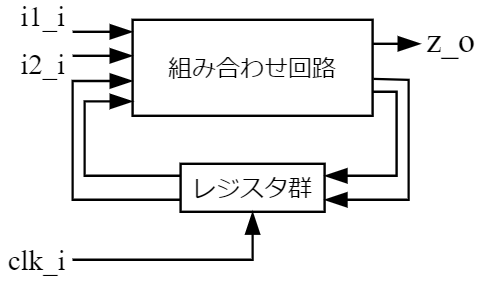

順序回路は図示すると,次のように組み合わせ回路とレジスタを組み合わせた回路となる.

組み合わせ回路の入力にレジスタの値が入力されているのが重要である.

ここで,順序回路のVerilogコードの例を挙げる.

次のコードでは,状態遷移を用いて上のロックの論理を記述しており,状態に応じてz_r(0:close, 1:open)の値を変化させている.

ifやcaseの人が把握しやすい条件分岐で表すことができ,慣れれば素早く書くことが可能だ.

また,次のVerilogは論理ゲートよりも抽象的な記述なので,レジスタ転送レベル(RTL:Resister Transfer Level)の記述と言われる.

module module1 (

input clk_i,

input i1_i,

input i2_i,

output z_o

);

reg z_r, state_r;

assign z_o = z_r;

parameter init_p = 0;

parameter meddle_p = 1;

parameter open_p = 2;

always @(posedge clk_i) begin

case (state_r)

init_p: z_r <= 0;

middle_p: z_r <= 0;

open_p: z_r <= 1;

endcase

end

always @(posedge clk_i) begin

case (state_r)

init_p: begin

if (i1_i == 0)

state_r <= init_p;

else

state_r <= state1_p;

end

middle_p: begin

if (i2_i == 0)

state_r <= state_r;

else

state_r <= open_p;

end

open_p: state_r <= state_r

endcase

end

endmoduleVerilogを書く目的⇒論理合成

上記のようなコードで論理回路を表せることを説明してきた.

しかし,ただ単にVerilogで論理回路を記述したいわけではなく,これらを論理ゲートで構成された回路(Gate Level)にするのが目的となる.

現代は便利なもので,Verilogのコード⇒論理ゲートで構成された回路の変換(論理合成と呼ばれる) は計算機が自動で行ってくれる.

また,論理の簡単化も論理合成の過程で行われる.

論理合成を経てVerilogで記述された論理が論理ゲートやフリップフロップのみの回路に変換されることで,論理回路の設計ができるようになる.

まとめ

VerilogはHDL(Hardware Description Language)の1種で,主に論理回路の(RTL:Resister Transfer Level)記述ができる.

Verilogで簡単に論理を記述することができ,論理合成を行うことでゲートレベルの回路に変換することができる.

次の記事 ↓↓↓